10 Minuten

Ein Team mehrerer US‑Universitäten und eine inländische Foundry haben eine neue monolithische 3D‑Chip‑Architektur vorgestellt, die Speicher und Rechenlogik vertikal stapelt, die Datenwege erheblich verkürzt und damit bedeutende Vorteile für KI‑Hardware verspricht. Der Prototyp — gefertigt in der US‑Foundry von SkyWater Technology — demonstriert die bisher höchste Dichte vertikaler Verdrahtung und zeigt klare, messbare Leistungs‑ und Effizienzvorteile gegenüber herkömmlichen 2D‑Designs.

Why stacking up changes everything

Moderne KI‑Systeme verlangen, dass sehr große Datenmengen zwischen Speicher und Verarbeitungseinheiten mit hoher Geschwindigkeit hin und her bewegt werden. Konventionelle Chips platzieren Logik und Speicher nebeneinander auf einer Ebene, sodass Daten lange, oft überlastete Wege zurücklegen müssen. Dieser Engpass — weithin bekannt als die „Speicherwand“ (memory wall) — begrenzt, wie schnell ein Chip seine Prozessoren mit Daten versorgen kann, selbst wenn diese Prozessoren immer schneller und zahlreicher werden.

Die monolithische 3D‑Integration verfolgt einen anderen Ansatz. Anstatt Komponenten über eine flache Fläche zu verteilen, bauen Entwickler viele ultradünne Leitungsschichten direkt übereinander auf und verbinden sie durch dichte vertikale Verdrahtungen. Diese Architektur verkürzt die langen Pfade, die die Datenbewegung verlangsamen, und ermöglicht es, Speicher unmittelbar neben den Rechenelementen zu platzieren, die ihn am dringendsten benötigen. Das Ergebnis ist eine wesentlich effizientere Kommunikation, höhere Durchsatzraten und ein deutlich geringerer Energieverbrauch pro Operation.

Zusätzlich reduziert die Nähe von Speicher und Recheneinheiten Latenz, verbessert die Bandbreitenausnutzung und senkt die Kommunikationskosten zwischen Rechenkernen. In der Praxis bedeutet das: schnellere Inferenz‑ und Trainingsläufe für KI‑Modelle, geringere Stromkosten im Rechenzentrum und verbesserte Möglichkeiten für leistungsfähige On‑Device‑Anwendungen im Edge‑Bereich.

From labs to a U.S. foundry: how they built the prototype

Das Projekt ist eine Kooperation von Forschenden der Stanford University, Carnegie Mellon University, der University of Pennsylvania, des MIT und SkyWater Technology — der größten in den USA ansässigen Pure‑Play‑Halbleiterfoundry. Im Gegensatz zu früheren 3D‑Ansätzen, bei denen bereits gefertigte Chips übereinandergestapelt wurden, verwendet diese Arbeit einen monolithischen Prozess: Jede neue Schicht wird direkt auf den darunterliegenden Lagen in einem kontinuierlichen Fertigungsablauf hergestellt.

Eine der technischen Hürden bei monolithischem Stapeln ist das thermische Budget — die maximale Temperatur, die ein Chip aushalten kann, ohne die bereits fertiggestellten unteren Schichten zu beschädigen. Das Team setzte deshalb auf Niedertemperatur‑Prozesse, die bestehende Schaltungen schonen, während zusätzliche Schichten aufgebracht und strukturiert werden können. Diese enge thermische Kontrolle ermöglicht Verbindungspunkte zwischen den Schichten, die deutlich kleiner und dichter sind als die groben Interposer, die in konventionellen gestapelten Systemen verwendet werden.

Die Herstellung des Prototyps innerhalb der SkyWater‑Foundry in Minnesota ist mehr als ein reiner Fertigungsmeilenstein — sie zeigt, dass fortgeschrittene 3D‑Chiparchitekturen von akademischen Prototypen in Prozesse übersetzt werden können, die mit inländischen kommerziellen Fab‑Standards kompatibel sind. Wie Mark Nelson, Vizepräsident bei SkyWater Technology, in Begleitgesprächen erläuterte, ist die Ermöglichung einer Produktion im kommerziellen Maßstab auf US‑Boden entscheidend für Zulieferkettenresilienz und nationale Technologie‑Führerschaft.

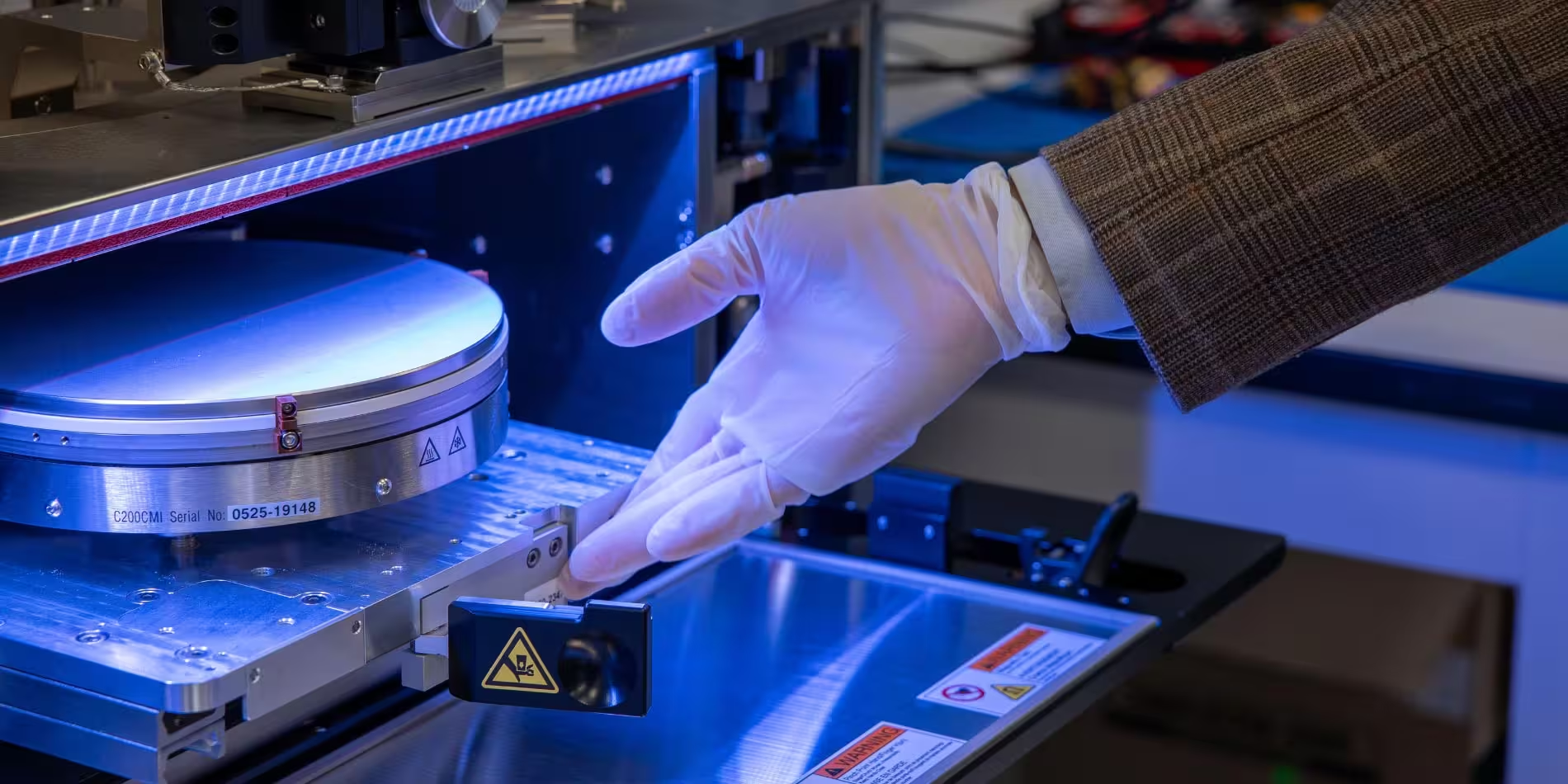

Zum Testen der neuen Chips nutzten die Forschenden eine spezielle Maschine, wie auf dem Bild zu sehen, um eine automatisierte elektrische Charakterisierung der Designs auf einer Wafer‑Platte durchzuführen.

Die Integration der gesamten Fertigungsschritte in einer US‑Foundry erleichtert zusätzlich die Einhaltung von Industriestandards, regulatorischen Vorgaben und Sicherheitsanforderungen, die bei sicherheitskritischen Anwendungen wie Raumfahrt, Verteidigung und kritischer Infrastruktur von Bedeutung sind. Darüber hinaus vereinfacht es die Skalierung zu einer zuverlässigen, qualifizierten Serienproduktion.

Measured gains and simulated potential

Frühe Hardware‑Tests des Prototyps zeigen signifikante Leistungszuwächse. Das Gerät der ersten Generation übertraf vergleichbare 2D‑Entwürfe in ausgewählten Benchmarks um etwa das Vierfache. Bei Simulationen höherer Designs — Chips mit zusätzlichen gestapelten Speicher‑ und Rechentiers — beobachtete das Team Verbesserungen von bis zu einer Größenordnung (und in bestimmten KI‑Workloads sogar Performance‑Sprünge von bis zu 12‑fach).

Besonders auffällig sind die Prognosen zum Energy‑Delay‑Product (EDP), einer kombinierten Metrik, die Geschwindigkeit und Energieverbrauch gewichtet. Durch die drastische Verkürzung von Datenwegen und die Vervielfachung vertikaler Interconnects können monolithische 3D‑Chips den Energiebedarf pro Operation deutlich senken und gleichzeitig den Durchsatz erhöhen. Die Forschenden sehen realistische Wege zu EDP‑Verbesserungen von 100‑ bis 1.000‑fach gegenüber aktuellen 2D‑Architekturen, vorausgesetzt, dass höhere Stacks und optimierte Designs implementiert werden.

Neben reinen Performance‑Metriken bieten verkürzte Datenpfade auch Vorteile für die Zuverlässigkeit und Systemarchitektur: geringere Kommunikationslatenzen erlauben neue Partitionierungs‑ und Parallelisierungsstrategien, während reduzierte Energie‑Peaks thermische Herausforderungen teilweise verringern können. Allerdings erfordern größere Stacks sorgfältige Optimierungen der physikalischen und logischen Schichten.

Science background: the memory wall and the miniaturization limit

Zwei langfristige Trends begrenzen die Entwicklung der Chipleistung. Erstens benötigen KI‑Workloads enorme, schnell bewegte Datensätze. Zweitens nähert sich die traditionelle Route der Halbleiterbranche — die Verkleinerung von Transistoren und das Aufbringen immer größerer Dichten auf einer flachen Die‑Fläche — harten physikalischen und ökonomischen Grenzen, die häufig als „Miniaturisierungsgrenze“ bezeichnet werden.

Das vertikale Stapeln adressiert beide Einschränkungen. Anstatt bloß mehr Transistoren in der gleichen Ebene unterzubringen, ergänzen Designer die dritte Dimension um zusätzliche Funktionalitätsschichten. Speicher kann über den Stack verteilt werden, sodass Rechenkerne schnellen, lokalen Zugriff auf die benötigten Daten erhalten. Diese Architektur bekämpft die Speicherwand direkt und bietet einen ergänzenden Pfad jenseits einfacher Transistor‑Skalierung.

Technisch gesehen ermöglicht die dritte Dimension auch heterogene Integration: unterschiedliche Speichertechnologien (z. B. SRAM, DRAM oder nichtflüchtige Speicher), spezialisierte Recheneinheiten (Tensor‑Cores, systolische Arrays) und I/O‑Schichten können physikalisch nahe zueinander positioniert werden. Das eröffnet neue Optimierungsräume für Latenz, Bandbreite und Energieeffizienz, erfordert jedoch koordinierte Design‑, Fertigungs‑ und Testmethoden.

Why U.S. domestic fabrication matters

Die Durchführung des gesamten Prozesses in einer US‑Foundry hat strategische Bedeutung. Die Arbeit demonstriert, dass fortschrittliche monolithische 3D‑Integration nicht nur eine Laborkuriosität ist, sondern mit Fertigungspraktiken produziert werden kann, die in den Vereinigten Staaten verfügbar sind. Für nationale Sicherheit, industrielle Wettbewerbsfähigkeit und die steigende Nachfrage nach inländischer KI‑Hardware ist diese Übersetzung in die industrielle Produktion wichtig.

Über die Fertigung hinaus gibt es eine Bildungs‑ und Fachkräftekomponente. Der Übergang zur vertikalen Integration wird Ingenieurinnen und Ingenieure benötigen, die in der Lage sind, 3D‑Systeme zu entwerfen, zu testen und zu optimieren. Die Projektpartner betonen Ausbildungsprogramme und multiinstitutionelle Zentren, die bereits Studierende integrieren und disziplinübergreifende Forschung fördern. Solche Initiativen helfen, die nächste Generation von Chipdesignern auf eine stärker vertikal orientierte Hardwarelandschaft vorzubereiten.

Zudem stärkt die heimische Produktion die Versorgungssicherheit: kürzere Lieferketten, geringere Abhängigkeiten von ausländischen Fertigungsstätten und bessere Kontrolle über sensible Technologien. All dies ist relevant für Industriepolitik, Förderprogramme und langfristige Investitionsentscheidungen.

Expert Insight

„Monolithische 3D‑Integration stellt ein grundlegendes Umdenken in der Architektur von Rechensystemen dar“, sagt Dr. Leila Martinez, Systemarchitektin an einem US‑Luft‑ und Raumfahrtforschungszentrum. „Wenn man den Speicher näher dorthin bringt, wo gerechnet wird, reduziert man sowohl Latenz als auch Energieverbrauch. Für KI‑ und Raumfahrtsysteme — in denen Nutzlast, Energie und Leistung eng begrenzt sind — kann das transformativ sein. Die Herausforderung wird sein, die Fertigung zu skalieren und gleichzeitig Fehlerquoten und thermisches Management unter Kontrolle zu halten.“

Ihre Einschätzung macht zwei Aspekte deutlich: Der Ansatz bietet starke Effizienzgewinne, bringt aber zugleich neue ingenieurtechnische Einschränkungen mit sich. Vertikale Stacks müssen Wärme über mehrere Ebenen ableiten, Ausbeuten bei höheren Dichten sichern und sich in bestehende Design‑ und Verifikationsökosysteme integrieren.

Remaining challenges and research directions

Obwohl der Prototyp bemerkenswerte Verbesserungen zeigt, bleiben mehrere technische Hürden, bevor monolithische 3D‑Chips zum Mainstream werden. Zu den wichtigsten Herausforderungen gehören:

- Thermal management: Wärme, die tief innerhalb eines gestapelten Dies entsteht, muss effektiv abgeführt werden, ohne empfindliche Schichten zu beschädigen. Neue Kühllösungen — von Mikrokanälen über thermische Vias bis zu innovativen Heat‑Spreadern — werden untersucht.

- Yield und Defekte: Dichtere Integration bedeutet, dass Fehler in einer einzelnen Schicht einen gesamten Chip beeinflussen können; Fertigungsprozesse benötigen sehr niedrige Defektdichten, um akzeptable Kosten zu gewährleisten. Methoden wie redundante Routen, fehlerkorrigierende Architekturen und verbesserte Inline‑Metrologie sind entscheidend.

- Design‑Tools und Methodologien: EDA‑Workflows und Verifikationstools müssen weiterentwickelt werden, um 3D‑Floorplanning, Routing und Timing‑Analysen zu unterstützen. Dies umfasst neue Abstraktionen, physikalisch korrekte Modelle und Simulationstools für thermische, elektromagnetische und mechanische Effekte.

- Materialien und Interconnect‑Zuverlässigkeit: Langzeitstabilität von vertikalen Vias, Dünnschicht‑Materialien bei Niedertemperaturprozessen und die Isolation zwischen Schichten müssen für kommerzielle Lebensdauern validiert werden.

Forschungsgruppen arbeiten aktiv an diesen Problemen. Thermische Simulationen, neue Kühlstrategien, Fehler‑Mitigationstechniken und Fortschritte in der Niedertemperaturverarbeitung sind Teil der laufenden Arbeiten. Industriepartner, staatliche Förderagenturen und vernetzte Forschungshubs unterstützen Bestrebungen, Laborfortschritte in zuverlässige Produkte zu überführen.

Praktische Lösungsansätze reichen von Prozessinnovationen (z. B. neue CVD‑ oder ALD‑Schritte bei niedriger Temperatur) über fortschrittliche Inline‑Messtechnik bis hin zu architektonischen Maßnahmen wie fehler‑toleranten Recheneinheiten, adaptivem Thermal‑Throttling und hierarchischen Speichermanagementstrategien. Ein koordiniertes Ökosystem aus Fertigung, Design‑Tools und System‑Software ist dabei entscheidend.

What this means for AI, space, and beyond

Für KI‑Entwickler eröffnet die engere Speicher‑Compute‑Integration die Möglichkeit, größere Modelle effizienter auszuführen, Betriebskosten in der Cloud zu senken und leistungsfähigere On‑Device‑Inference für Edge‑ und Mobile‑Systeme zu ermöglichen. Modelle, die bislang nur in Rechenzentren praktikabel waren, könnten lokal, latenzarm und energieeffizienter laufen.

In Raumfahrt‑ und Verteidigungsszenarien, in denen Energie und Volumen stark begrenzt sind, könnten monolithische 3D‑Chips leistungsfähigere Sensorik, Datenverarbeitung und Autonomie an Bord erlauben, ohne signifikant zusätzliche Masse oder Energie zu beanspruchen. Solche Chips könnten damit neue Missionstypen und fortschrittlichere autonome Systeme ermöglichen.

Die Ankündigung signalisiert außerdem Dynamik für ein breiteres inländisches Halbleiterökosystem: Universitäten bilden Studierende aus, Foundries passen ihre Prozessflüsse an, und staatliche wie industrielle Förderungen zielen darauf ab, die Abhängigkeit von ausländischer Fertigung zu verringern. Zusammengenommen weisen diese Elemente auf eine Zukunft hin, in der US‑basierte Forschung schneller in produktionsreife Hardware überführt wird.

Kurz gesagt: Der monolithische 3D‑Chip‑Prototyp ist ein bedeutender Schritt. Er beseitigt nicht alle technischen Herausforderungen über Nacht, bietet aber einen klaren, herstellbaren Pfad zu Architekturen, die langjährige Engpässe aufbrechen können. Für KI‑Hardware‑Designer, Chip‑Hersteller und politische Entscheider stellt die Arbeit einen vielversprechenden Ansatz dar, um durch das Umdenken in der dritten Dimension sowohl Leistung als auch Energieeffizienz zu gewinnen.

Quelle: scitechdaily

Kommentar hinterlassen